Applied Surface Science 7341 (2001) 1-5

www.elsevier.com/locate/apsusc

## A novel laser trimming technique for microelectronics

M. Meunier<sup>a,b,\*</sup>, Y. Gagnon<sup>b</sup>, Y. Savaria<sup>b,c</sup>, A. Lacourse<sup>a,b</sup>, M. Cadotte<sup>a</sup>

<sup>a</sup>Département de Génie Physique, École Polytechnique de Montréal, Case Postale 6079, succ. Centre-Ville, Montreal, Que. H3C 3A7, Canada

<sup>b</sup>LTRIM Technologies, 440 Blvd Armand Frappier, suite 140, Laval, Que. H7V 4B4, Canada

<sup>c</sup>Département de Génie Électrique et Génie Informatique, École Polytechnique, CP 6079,

succ. Centre-Ville, Montreal, Que. H3C 3A7, Canada

#### Abstract

3

4 5

6 7

8

9

10

11 12

A novel laser trimming technique, fully compatible with conventional CMOS processes, is described for analogue and mixed microelectronics applications. In this method, a laser beam is used to create a resistive device by melting a silicon area, thereby forming an electrical link between two adjacent p–n junction diodes. These laser diffusible resistances can be made in less than a second with an automated system, and their values can be in the range 100  $\Omega$  to a few megaohms, with an accuracy of 50 ppm, by using an iterative process. In addition, these resistances can also be made to possess a TCR (temperature coefficient of resistance) close to 0. We present the method used to create these resistances, the main device characterization and some insight on process modeling. © 2001 Published by Elsevier Science B.V.

*Keywords:* Laser trimming; Analogue microelectronics; Resistance

### 23 1. Introduction

24 In spite of the steady progress of digital electronics, 25 nowadays electronic systems often contain significant analogue sub-systems, because their connection to the 26 27 external world often implies dealing with analogue signals. Actually, the general model of a digital core 28 29 with analogue external interfaces is found in most 30 telecommunication, digital signal processing and con-31 trol applications. While the growing transistor counts available with digital integrated circuits that can 32 33 absorb all functions of many electronic systems, ana-34 logue sub-systems get integrated at a much slower pace, due primarily to their component accuracy 35 requirements. For systems that need high accuracy, 36 system designers are usually forced to use some sort of 37 trimming. This may sometimes be avoided by relying 38 on a limited number of high accuracy components, 39 which tend to be relatively expensive, by hiding from 40 the user some sort of interior trimming, or by referring 41 all key performance parameters to a single device that 42 determines system accuracy. For instance, Taylor and 43 Hanlon [1] describe the design of a 12-bit DAC 44 (digital to analogue converter) implemented using 45 wafer laser trimming. In most approaches, trimming 46 involves the modification of the impedance or resis-47 tance of integrated components through the use of 48 laser, ion or electron beams [2-14]. The methods 49 based on laser ablation of thin [2,3,6] or thick [4–6] 50 films, mesh trimming [7] and polysilicon link making 51 [8,9] all require an additional process step to deposit 52 the resistive film. Laser polysilicon link making even 53

<sup>&</sup>lt;sup>\*</sup> Corresponding author. Present address: Département de Génie Physique, École Polytechnique de Montréal, Case Postale 6079, succ. Centre-Ville, Montreal, Que. H3C 3A7, Canada. Tel.: +1-514-340-4711, ext: 4971; fax: +1-514-340-3218. *E-mail address*: meunier@phys.polymtl.ca (M. Meunier).

<sup>1 0169-4332/01/\$ -</sup> see front matter © 2001 Published by Elsevier Science B.V.

<sup>2</sup> PII: S0169-4332(01)00622-5

M. Meunier et al. / Applied Surface Science 7341 (2001) 1-5

requires masking of the polysilicon film prior to 54 implantation. Polymer trimming [10], in which poly-55 56 mer conductivity is changed by exposition to infrared light, not only requires an additional material layer, 57 but is also very slow. Pulsed voltages [11,12] and 58 floating gate [13] methods present the advantage of 59 compensating for the resistance of the package pins. 60 Even if integrated circuits can be trimmed after packa-61 ging, this method requires additional pads to provide 62 63 the electrical stimulus used to trim, which consumes significant die space, particularly with low pin count 64 analogue or mixed signal components. In most tech-65 niques presented above, the additional process steps 66 67 increase cost and consume significant die area, which limits their flexibility and usefulness. 68

The method presented in this paper is an extension 69 of the laser-induced diode linking that was originally 70 proposed for wafer-scale integration [15–17]. By a 71 careful iterative approach, this diode linking method is 72 used for impedance tuning of semiconductor resis-73 74 tances. This novel trimming method produces laser diffusible resistances that can be very accurate, uses 75 very small die area, and can be integrated into any 76 77 existing CMOS process without any additional masking step. A patent disclosing the detailed device 78 structure and creation method has been accepted at 79 the US and Canadian patent offices, and was also 80 submitted as a PCT patent [14]. 81

# 82 2. Principle of the laser trimming method and83 experimental setup

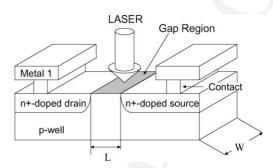

84 The laser trimming technique is applied to a device 85 structure shown in Fig. 1. Put simply, this structure is a MOSFET with no gate contact, fabricated with any 86 conventional CMOS process. For an n-type resistor, 87 the device structure consists of two highly doped 88 regions, separated by a distance L, and formed by 89 implantation into a p-well, resulting into two p-n 90 91 junctions facing each other. The device has a width W and the electrical connections to the structure are 92 93 formed using contacts. Finally, an oxide layer protects the device. Complementary doping types are used for 94 a p-type resistor. Before performing laser trimming, 95 96 the only currents that can flow through the device are leakage currents from the p-n junctions to the sub-97 strate, resulting essentially in an open circuit. Focus-98

Fig. 1. Schematic cross-section of the laser diffusible resistance.

ing a laser beam on the gap region between the two 99 junctions melts the silicon, resulting in dopant diffu-100 sion from the highly doped regions to the lightly 101 doped gap region. Upon removal of the laser light, 102 the silicon freezes and solidifies, leaving the diffused 103 dopants in a new local distribution, which may form 104 an electrical link between the highly doped regions. 105 This laser-diffused link constitutes the trimmed resis-106 tance. Tight control of process parameters is necessary 107 to efficiently create these laser diffusible resistances, 108 while avoiding damage to adjacent devices and struc-109 tures. These parameters are the laser spot size, pulse 110 duration, laser power, number of laser exposures and 111 position of the laser spot relative to the device. By 112 varying these parameters between each laser irradia-113 tion, one can accurately tune the device. The laser 114 trimming system used comprises a Coherent Innova 115 90 5 W argon ion laser, running all lines for maximum 116 possible power, an acousto-optic modulator (AOM) 117 from Neos technologies implemented as a high-speed 118 shutter, and a Klinger X-Y-Z positioning table. The 119 laser beam is focused on the device structure to a spot 120 2 µm in diameter, and the system is computer con-121 trolled to speed up the process. 122

#### 3. Device characterization

While the results presented here were obtained on 124 devices made with the MITEL 1.5 µm technology 125 with dimensions  $L = 1.7 \,\mu\text{m}$  and  $W = 6 \,\mu\text{m}$ , we have 126 successfully verified that the method works for a 127 0.35 µm technology. A large number of laser diffu-128 sible resistances, with a 100% yield, have been created 129 using a prototype integrated circuit comprising many 130 target sites on the same circuit. 131

123

M. Meunier et al. / Applied Surface Science 7341 (2001) 1-5

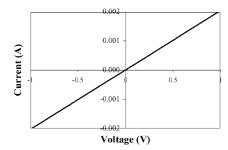

Fig. 2. Typical *I*–*V* characteristic of a laser diffusible resistance (value =  $492 \Omega$ ) at room temperature.

132 Current-voltage characteristics were measured using a Hewlett Packard 4155A semiconductor para-133 meter analyzer. I-V characteristics for all devices 134 produced by our iterative laser trimming process show 135 excellent linear behavior at potential differences smal-136 ler than 0.3 V. Resistance values from 100  $\Omega$  to as high 137 as a few megaohms, with accuracy of 50 ppm, can be 138 made easily. Typical I-V characteristic for a 492  $\Omega$ 139 device is shown in Fig. 2. 140

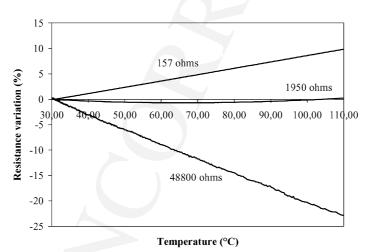

Resistance as a function of temperature was mea-141 sured using a Hewlett Packard 34401A digital multi-142 143 meter and a Yamato Scientific America DX300 oven to control the device temperature. Fig. 3 depicts 144 typical resistance variations as a function of tempera-145 ture. Resistances having values lower than  $1.5 \text{ k}\Omega$ 146 present a positive temperature coefficient, and those 147 148 with values higher than  $3 k\Omega$  present a negative 149 temperature coefficient. For a gap of 1.7 µm and a width of 6  $\mu$ m, there exists a resistance for which the temperature coefficient is close to 0. This value is around 2 k $\Omega$  in this case, and it is expected to vary with device geometry and doping levels. 153

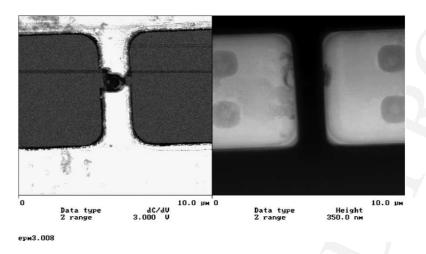

Fig. 4 shows images produced with an atomic force 154 microscope (AFM) and a scanning capacitance micro-155 scope (SCM) (Digital Instruments, Dimension 3100 156 model) of a laser-diffused resistance, where all outer 157 dielectric layers have been removed by an HF etch. 158 Five laser pulses were used in this experiment and the 159 laser parameters were maintained at 0.75 W (incident 160 on the surface of the chip) and 1 µs duration. While the 161 AFM image reveals no significant deformation of the 162 p-well, the SCM image shows clearly that dopants, as 163 represented by dark gray, have diffused from the two 164 n<sup>+</sup> regions into the p-channel. The diffused region is 165 about 1 µm in size. 166

#### 4. Process modeling

Modeling this process involved a time-dependent 168 three-dimensional (3D) calculation of the temperature 169 due to the laser irradiation, followed by a dopant 170 distribution calculation using Fick's law. A simple 171 model must include the effects of the laser power, 172 beam waist and exposure time as well as the geometric 173 characteristics of the initial structure. Device charac-174 teristics can then be evaluated by solving the three 175 differential coupled equations to obtain the 3D dis-176

Fig. 3. Resistance variation in percent (relative to the 30  $^{\circ}$ C value) as a function of temperature for three laser diffusible resistances with nominal values at 30  $^{\circ}$ C of 157, 1950 and 48 800  $\Omega$ .

3

167

M. Meunier et al. / Applied Surface Science 7341 (2001) 1-5

Fig. 4. SCM (left) and corresponding AFM image (right) of diffused resistance. The n-channel is clearly visible on the SCM image, whereas topography (AFM) reveals no significant deformation of the p-well.

tributions of electron and hole concentrations, as well

as the electric field in this device presenting a nonuniform dopant distribution. In addition, modeling

must also include the possibility of varying the laser

beam location and power from pulse to pulse to obtain

the desired device characteristics.

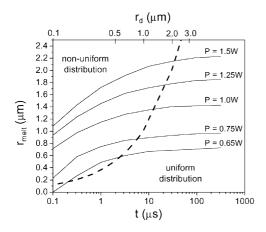

Some insight on process modeling can be obtained 183 by using careful approximations. We consider the 184 effect of a focused laser beam incident on an n<sup>+</sup>-p-185 n<sup>+</sup> silicon structure, resulting in the diffusion of 186 187 dopants into silicon. Because the diffusion length of dopants in liquid Si is 4 orders of magnitude higher 188 than that of crystalline Si [19], we assume that only 189 190 dopants in the silicon melt diffuse. During the laser pulse, the silicon melt dimension increases and then 191 192 decreases as the pulse ends. Therefore, we propose that only the maximum melted region (as denoted by 193  $r_{\text{melt}}$  on the Si surface) has to be determined in the 194 temperature calculation; the dopants located outside 195 this region are assumed to be immobile. As the pulse 196 duration t increases, dopants with a diffusion coeffi-197 198 cient D will have more time to diffuse over a length of  $r_D = 2\sqrt{Dt}$  in the entire melted region yielding a more 199 uniform dopant distribution. For instance, arsenic 200  $(D = 3.3 \times 10^{-4} \text{ cm}^2/\text{s} \text{ in liquid Si [19]})$  was the 201 major dopant in the n<sup>+</sup> regions of the structures 202 203 investigated and  $r_D(m) = 0.4\sqrt{t(s)}$ , suggesting that laser pulses of a few microseconds are required for 204 uniform dopant distribution over a fraction of a micro-205 meter. 206

The calculation of the temperature distribution 207 resulting from a focused laser beam is based on a 208 method by Bäuerle [18] and Cohen et al. [16]. The 209 heat diffusion equation is solved in the case of a 210 Gaussian beam of radial symmetry and exponentially 211 decaying optical absorption. The pulse is rectangular in 212 time. The temperature dependence of the thermal 213 conductivity is taken into account via a Kirchhoff 214 transformation. The solution of this problem is in 215 the form of a temporal integral to be solved numeri-216 cally. In the method proposed by Cohen et al., optical 217 absorption and heat diffusion coefficient do not vary 218 with temperature. Furthermore, the latent heat of fusion 219 is not incorporated into the calculations and only the 220 steady state problem is solved (though it is pointed out 221 that the solution of the time-dependent problem can be 222 obtained merely by changing the integration limits). 223

We extend Cohen's method to the time-dependent 224 problem, including latent heat of fusion and partially 225 taking into account temperature-dependent reflectivity, 226 optical absorption and heat diffusion coefficient. This 227 is done within an adiabatic approximation [20] where 228 the time evolution of the temperature can be monitored 229 by separating the time integral into small segments. 230 After each temperature increment, the silicon proper-231 ties are adjusted to the new temperature before the next 232 temperature jump is calculated. In this way, the impor-233 tant variation of silicon properties as a function of 234 temperature, particularly at the solid/liquid transition, 235 are partially included. As for the latent heat of fusion, 236

M. Meunier et al. / Applied Surface Science 7341 (2001) 1-5

Fig. 5. Maximum silicon melt radius  $r_{melt}$  as a function of pulse duration t and laser power. Laser 1/e radius is 1.0 µm. The dashed line separates the uniform dopant distribution from the nonuniform distribution.

an internal loop in the numerical algorithm insures that 237 it is taken into account. When the temperature reaches 238 the melting point  $(T_f)$ , it is maintained at this value and 239 240 the subsequent temperature rises are converted into 241 enthalpy until sufficient energy is accumulated [21], i.e. when the enthalpy of silicon reaches the latent heat 242 of fusion. The next temperature calculations are then 243 made as before, with the exception that the material 244 properties are those of liquid silicon. 245

246 Fig. 5 shows the results of numerical calculations of  $r_{\rm melt}$  as a function of laser duration for different laser 247 powers at a fixed waist of 1.0 µm. For a laser power of 248 249 0.75 W and 1  $\mu$ s, the calculation is in relatively good agreement with the SCM results of Fig. 4. In addition, 250 251 conditions for uniform dopant distribution are located on the right side of the dashed line corresponding to 252  $r_{\text{melt}} = r_D$ . Fig. 5 can then be used to determine the 253 laser power and time width t of the various laser 254 exposures in an iterative process to fine-tune the 255 256 dopant distribution to yield a specific resistance value.

#### 5. Conclusion 257

Laser diffusible resistances can be made accurately 258 259 by an iterative process to obtain resistance values between  $100 \Omega$  and a few megaohms. This new 260 trimming technique is compatible with CMOS pro-261 cesses and can accurately produce resistances in less 262

than a second. Further studies are being performed on 263 process optimization and modeling, as well as on 264 applications of these resistances in analogue micro-265 electronic circuits. These studies will be the subjects 266 of future publications. This technique is being imple-267 mented for high-volume production of integrated 268 circuits by LTRIM technologies. 269

#### Acknowledgements

The authors are grateful to J.P. Lévesque and to M. 271 Ducharme for their help in the development of the 272 technique and to Digital Instruments for their SCM/ 273 AFM images of diffused resistances. 274

#### References

- [1] S.S. Taylor, P.J. Hanlon, in: E.S. Sinencio (Ed.), Proceedings 276 of the 26th Midwest Symposium on Circuits and Systems, 277 Western Periodicals, North Hollywood, CA, 1983, pp. 218-278 222

- [2] P. Fehlhaber, Solid State Technol. 14 (1971) 33.

- [3] R.K. Waits, Thin Solid Films 16 (1973) 237.

- [4] M. Oakes, Opt. Eng. 17 (1978) 217.

- [5] R.L. Waters, M.J. Weiner, Solid State Technol. 13 (1970) 43.

- [6] S. Schiller, U. Heisig, S. Panzer, Solid State Technol. 18 (1975) 38.

- [7] J. Shier, IEEE J. Solid-St. Circ. 23 (1988) 1004.

- [8] D.L. Parker, F.-Y. Lin, D.-K. Zhang, IEEE Trans. Comp. Hyb. Manuf. Technol. (CHMT) 7 (1984) 438.

- [9] D.L. Parker, H. Weiling, IEEE Trans. Semiconduct. Manuf. 3 (1990) 80.

- [10] T. Badri Narayana, K. Ramkumar, M. Satyam, J. Phys. D 25 (1992) 717.

- [11] T. Tobita, H. Takasago, IEEE Trans. Comp. Hyb. Manuf. Technol. 14 (1991) 613.

- [12] D.W. Feldbaumer, J.A. Babcock, V.M. Mercier, C.K.Y. Chun, IEEE Trans, Electr. Dev. 42 (1995) 689.

- [13] E. Säckinger, W. Guggenbühl, IEEE J. Solid-St. Circ. (SC) 23 (1988) 1437.

- [14] Y. Gagnon, M. Meunier, Y. Savaria, US Patents 09/332,059 and PCT#06042-002-WO-1 (2001).

- [15] S.S. Cohen, P.W. Wyatt, G.H. Chapman, J.M. Canter, IEEE Trans. Electr. Dev. 35 (1988) 1533.

- [16] S.S. Cohen, P.W. Wyatt, G.H. Chapman, J.M. Canter, IEEE Trans. Electr. Dev. 36 (1989) 1220.

- [17] I.D. Calder, H.M. Naguib, IEEE Electr. Dev. Lett. 6 (1985) 557.

- [18] D. Bäuerle, Laser Processing and Chemistry, 3rd Edition, Springer, Berlin, 2000.

- [19] H. Kodera, Jpn. J. Appl. Phys. 2 (1963) 212.

- [20] D.M. Kim, R.R. Shah, D.L. Crosthwait, J. Appl. Phys. 51 (1980) 3121. 312

- [21] J.E. Moody, R.H. Hendel, J. Appl. Phys. 53 (1982) 4364.

5

270